# Design Alternatives For A 4-Bit Universal Shift Register Using Clock Pulse Sense Latch.

Suraj pattanaik<sup>1</sup>, Suraj kumar samal<sup>2</sup>

<sup>1</sup>(ECE, Center for advanced post graduate studies, BPUT, India) <sup>2</sup>(ECE,Asst.Prof.,Gandhi Institute for Education & Technology, India)

**Abstract:** This paper proposed the design of 4-bit universal shift register using a low power area reduced speed improved clock pulse generator and clock sense pulse latch. The proposed 4-bit universal shift register consists of two section of operation one section included pulse latch and another section for the control operation like right shift, left shift and parallel loading. These operations of the universal shift register executed by 4\*1 MUX. All the MUX design using PTL logic and the clock pulse generator is designed using inverted inverter logic and pass transistor based AND gate circuit. The proposed 4-bit universal shift register increased the speed with low power consumption. The 4-bit universal shift register is designed and tested by using cadence virtuoso simulation tool in 180nm technology at a supply voltage of 1.8v for pulse latch and 2.5v for 4\*1 MUX.

**Keywords:** low power, clock pulse generator, 180nm, cadence virtuoso, pass transistor logic, area-efficiency, MUX design, shift register.

#### I. Introduction

Due to the increment of portable system and rapide devllopment in electronic sectore a low power and less area and speed improved device is necessaryto archives this gole .a low power speedimproved 4-bit univarsal shift registerhas beeen designed for different electronics application like data processing ,data counter ,computer memory element[1].the latches and flipflop are the basic storage element of all digitl electronics circuits.but for operating a latch a clock pulse generator is required.Due to the the clock pulse generatorproduced squezied clock pulse ,the latches are act as edge triggerd flipflop[1].

The advantages of the clock pulse latch over flipflop is it conssumes less area and low power and due to it operate with a shorter length clock pulse it provide faster operation ratherthan flip-flop.so the univarsal-shift register are designed for load or retrive the data in any mode .like either (serial and parallel ) by shifting it either towords right or towords left.a univasal shift register can conduct 3-mode of operation left shift, right shift and parallel load of operation with the help of two select line S1,S0,which is connected to the control module the control modul contain 4\*1 MUX.

In order to operate the univalsal shift register in asppecific mode ,it must first select the mode.to accomplish mode selection the univalsal shift register uses a set of two selector switches S1,S0eatch permutation of the switches corresponds to a loading /input mode[2].

| TABLE I |    |               |  |  |  |

|---------|----|---------------|--|--|--|

| S0      | S1 | Function      |  |  |  |

| 0       | 0  | Parallel load |  |  |  |

| 0       | 1  | Left Shift    |  |  |  |

| 1       | 0  | Right Shift   |  |  |  |

| 1       | 1  | No Change     |  |  |  |

#### **Clock Pulse Generator**

### **II. Basic Concept**

Clock Pulse Generator (CPG) is the main consideration for operating a clock sense pulse latch .CPG is basically designed using clock pulse circuits which are connected through a metal path back to back serially, like first clock pulse generator output feed to next input of the clock pulse circuit. The CPG generate clock pulse having shorter in length due to this property of the CPG more data can shifted through corresponding clock sense pulse latch rather than other conventional model.so the produced timing signal of the CPG reduced the delay period between to back to back clock pulses. The CPG is use as a trigger circuit for different applications like shift register, ring counter, frequency divider and many synchronizing circuit operations.

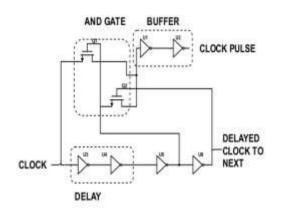

Fig. 1(a) Schematic daigram of single bit clock pulse generator [5]

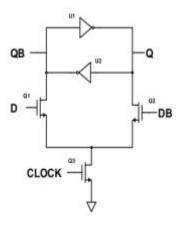

#### **Clock Sense** Pulse Latches

Latches are generally used to store base-2 number data in an asynchronous sequential system. Clock pulse generator is the circuit which is used to build shift register and other electronic circuit through a clock sense pulse latch. When the time sensitivity determine by the width of the clock waveform then only the pulse latch can store data. For operating a pulse latch a clock pulse latch is required .the clock pulse is said to be set when the rising edge of the clock pulse towards the pulse latch and is to be in hold state during the falling edge is towards the pulse latch. A clock tree is requires for operating a higher bit and to triggering the latch.

Fig.1(b) Schematic diagram of the SSASPL latch [1]

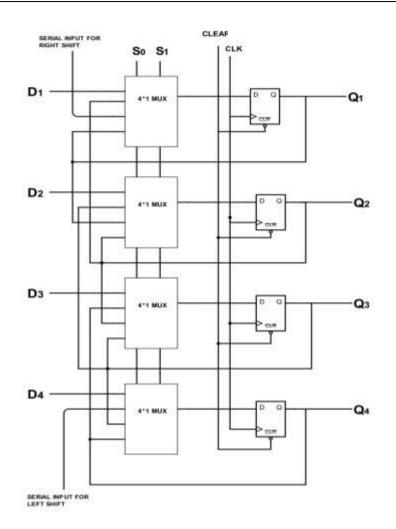

Universal Shift Register can be arranged to load and/or redeem the data in any mode (either serial or parallel) by shifting it either towards right or towards left. A universal shift register is an integrated logic circuit that can carry data in three different modes. Like a parallel register it can load and communicate data in parallel. Like shift registers it can load and carry data in serial fashions, through left shifts or right shifts. Moreover, the universal shift register can merge the potential of both parallel and shift registers to achieve tasks that neither basic type of register can perform on its own. For instance, on a particular job a universal register can loaddata in series (e.g. through a sequence of left shifts) and then transmit/output data in parallel. [3]

Universal shift registers, like other types of registers, are used in computers as memory elements. Although other types of memory devices are used for the logical storage of very large amount of data, from a digital system point of view when we say computer memory we understand registers. In reality, all the operations in a digital system are execute on registers such operations incorporate multiplication, division, and data transfer.

For the universal shift register to work in a particular mode, it must first select the mode. To realize mode selection the universal register uses a set of two selector switches, S1 and S0. As shown in Table 1, each permutation of the switches agree to a loading/input mode.

**Fig.1(c)** Architecture of universal shift registers[2]

# III. Proposed System

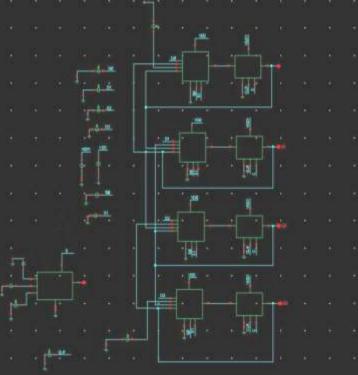

A universal shift register can conduct 3-mode of operation like left shift, right shift, parallel loading with the help of two select line S1and S0 which is connected through control module .the control module contains 4\*1 MUX.For constructing a 4-bit universal shift register required component are single clock pulse generator (SCPG), static sense amp shared pulse latch(SSASPL) and 4\*1 MUX.

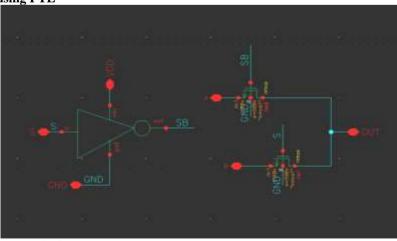

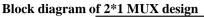

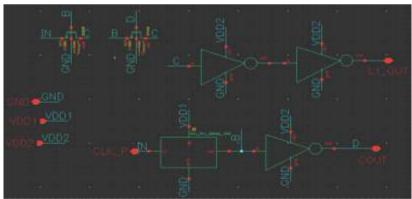

2\*1 MUX design using PTL

Fig.2(a) Schematic diagram of a 2\*1 MUX design using PTL

The Fig.2 (a) shows the schematic diagram of a2\*1 MUX design having 4 transistor, two NMOS and one inverter circuit using PTL (pass transistor logic). All the design done using labeling technique in cadence virtuoso tool.

Fig.2(b)Block diagram of a 2\*1 MUX design using PTL

The Fig.2 (b) shows the block diagram of a 2\*1 MUX design having 4 transistor. Here A,B are the data input pin "S" pin is for the select line "OUT" pin is for the output pin, "GND" pin for ground and "VDD" pin is for biasing voltage supply.

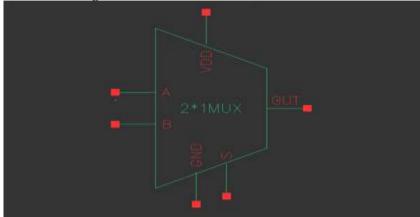

# 4\*1 Mux design using PTL

Fig.2(c)Schematic diagram of a 4\*1 MUX design using PTL

The Fig.2(c) shows the schematic diagram of a 4\*1 MUX design having 12 transistor. The 4\*1 MUX design consist of three number of 2\*1 MUX. Here the S0 and S1 are the select lineand all the design done using labeling technique in cadence virtuoso tool.

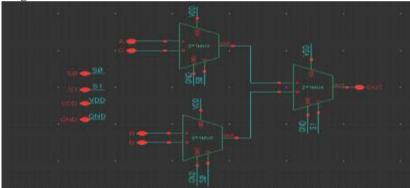

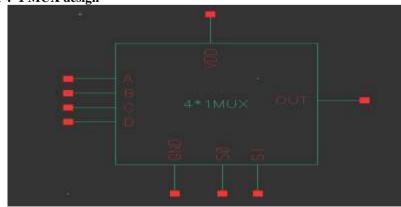

### Block diagram of 4\*1 MUX design

Fig.2(d)Block diagram of a 4\*1 MUX design using PTL

The Fig.2 (d) shows the block diagram of a 4\*1 MUX design having 12 transistor. Here A,B,C,D are the data input pin S1,S0 pin are for the select line "OUT" pin is for the output pin, "GND" pin for ground and "VDD" pin is for biasing voltage supply.

#### Design of a clear pin for Univarsal-Shiftregister

Fig.2(e)Schematic diagram of a SSASPL latch with clear pin

The Fig.2(e)shows the Schematic diagram of a SSASPL(static differential sense amp shared pulsed latch) with clear pin. Here a clear pin introduced when it activated it clear the previous data stored in the latch. A NMOS is connected to the "QB" output pin of the SSASPL latch all the design done using labeling technique in cadence virtuoso tool.

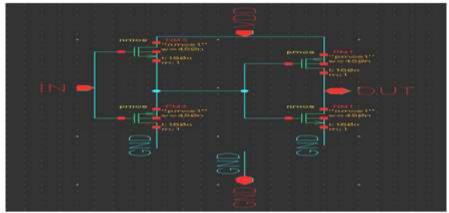

### Proposed single clock pulse generator

The proposed single clock pulse generator (SCPG) is the combination of different circuits stage like complimentary pass transistor logic base AND gate circuit, inverted inverter base delay circuit and some buffer circuits. In inverted inverter circuit consists of two NMOS and two PMOS transistor the 2 NMOS transistor having the width of 500nm.and 2 PMOS transistor having the width of 500nm.and each inverter circuit consists of 1NMOS and 1PMOS transistor having width of 500nm. The input signal v-pulse is supplied to the inverted inverter circuit and the output was further feed to the inverter circuit. The single clock pulse circuit operates in two VDD supplies, one is connected to the inverted inverter delay circuit and other is connected to all inverter circuits. The VDD supply to the inverted inviter delay circuit is 2.5V and 1.8V DC supply is given to the inverter circuits. All the connection of the circuit element is designed using labelling technique in Cadence Virtuoso. The length of each transistor is 180nm.

Fig. 2(f) Schematic diagram of the proposed single clock pulse circuit.

#### Delay circuit design

The principle of delay circuit is based on inverted inverter logic. Here the inverted inverter [14] delay circuit contains 2 NMOS and 2 PMOS transistors of 500nm width.

Fig.2 (g) Schematic diagram of inverted inverter delay circuit. [14]

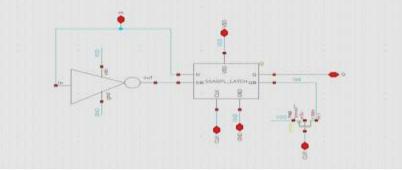

Fig.2(h)Testing diagram of Universal shift register

TheFig.2(h)shows the Testing diagram of a Proposed 4-bit universal shift register. Here the biasing voltage VDD for the 4\*1 MUX is 2.5v and the biasing voltage VDD for the latch circuit is 1.8v.here a SCPG connected to 4 number of latches using labelling technique in Cadence Virtuoso. If the number of register increases then a clock pulse generator (CPG) will be required for overcome the timing miss match of the latches.

# **IV. Result Analysis**

After designing the 4-bit universal shift register transient response has been analyzed and average power and area is calculated. For testing of the proposed 4-bituniversal shift register two different range of v-pulses are required, one for clock pulse generator and the other for the latch circuit. All connections of the latch and clock pulse generator circuit are done by labelling technique.

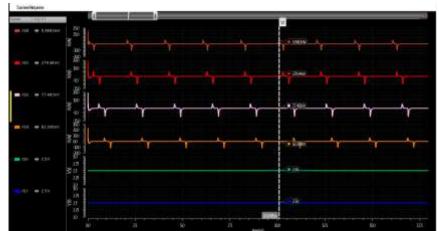

Fig.3(a)Transient response of the proposed 4-bit universal shift register in no change operation

The proposed 4-bit universal shift register is designed and tested using Cadence Virtuoso version (6.1.6-64b.500.4). The fig 3(a) shows the transient response of the proposed 4-bit universal shift register for no change operation. The clock pulse of 2ns and input of 40ns time period has been given as input.

Fig.3(b)Transient response of the proposed 4-bit universal shift registers for left shift operation

The Fig.3(b)shows the transient response of the proposed 4-bit universal shift register for left shift operation. The clock pulse of 2ns and input of 40ns time period has been given as input.

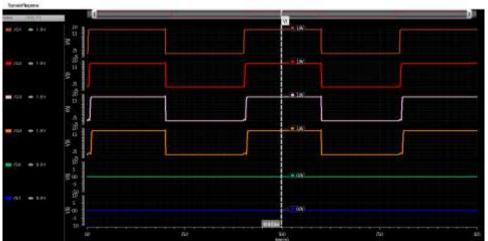

Fig.3(c)Transient response of the proposed 4-bit universal shift registers for parallel load operation

The Fig.3(c)shows the transient response of the proposed 4-bit universal shift register for parallel load operation. The clock pulse of 2ns and input of 40ns time period has been given as input.

Fig.3(d)Transient response of the proposed 4-bit universal shift register for right shift operation

The Fig.3(d)shows the transient response of the proposed 4-bit universal shift register for right shift operation. The clock pulse of 2ns and input of 40ns time period has been given as input.

# Power measurement of the proposed design

The average power calculation is done in cadence virtuoso ADEL calculator window and measured for different frequencies like 500MHz and 100MHz for the proposed 4-bit universal shift register.

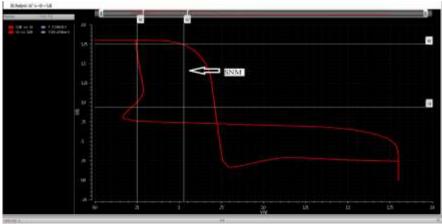

# V. Noise Analysis

Due to noise in shift register many time some output data bit may be flip one to zero or zero to one .in this situation we cannot find out the desired output.to overcome this situation we need to calculate noise margin. The static noise margin (SNM) is found out by introducing DC noise at node Q (or Qb) [13].in fig 5(a) shows the butterfly plot of the latch design .here the two crossing point at the tips of the lobes are stable points and the center crossing is a Meta stable point. The SNM is interpreted as the length of the side of the largest square inside the butterfly lobe .if one lobe is smaller than other, then the cell is said to be imbalanced and the SNM is defined as the length of the largest square that fits inside the smaller of the two lobes .[13]

Fig.4 Butterfly plot of the SSASPL design

The fig.4 shows the SNM (static noise margin) of the SSASPL design and the measured SNM for the design is 850mv.

# VI. Performance Analysis

The performance analysis of 4-bit universal shift register in 180nm technology has been provided in table number 2.

| operation mode | Average power[mW] |        | Delay(ps) | Total transistor count   |

|----------------|-------------------|--------|-----------|--------------------------|

|                | 100MHz            | 500MHz |           | in 4-bit universal shift |

|                |                   |        |           | register                 |

| parallel load  | 0.316             | 0.675  | 6140      |                          |

| Left shift     | 0.386             | 0.690  | 958       |                          |

| Right shift    | 0.392             | 0.688  | 3140      | 92                       |

| no change      | 0.291             | 0.649  |           |                          |

# **TABLE II**

| Parameters  | CMOS   | Proposed Design |  |  |

|-------------|--------|-----------------|--|--|

| Power(mW)   | 67.2   | 0.678           |  |  |

| Delay(pS)   | 532.51 | 3240            |  |  |

| No of       | 216    | 92              |  |  |

| Transistors |        |                 |  |  |

#### VII Comparison Analysis

#### VIII. Conclusion

In this paper a new clock pulse generator (CPG) and a 4-bit universal shift register has been proposed. The proposed 1-bit CPG consist of 12 transistors. And the proposed 4-bit universal shift register design consists of 92 transistors. The power and speed of 4-bit universal shift register has been calculated. The speed and the power consumption is better than other conventional flip-flop based universal shift register.

#### References

- Byung-Do Yang, "Low-Power and Area-Efficient Shift Register Using Pulsed Latches," IEEE transactions on circuits and [1]. systems—I: regular papers, vol. 62, no. 6, June 2015, pp. 1564-1571

- Heranmoy Maity, Arindam Biswas, Anup Kr. Bhattacherjee, Anita Pal, "Design of Quantum Cost Efficient 4-Bit Reversible [2]. Universal Shift Register," Devices for Integrated Circuit (DevIC), 23-24 March, 2017, Kalyani, India, 2017, pp. 44-47

- [3]. Tanushree Doi, Vandana Niranjan,"Low power and high performance ring counter using pulsed latch technique," International Conference on Micro-Electronics and Telecommunication Engineering, 2016, pp. 584-586.

- [4]. Wei Jin, Seongjong Kim, Weifeng He, Zhigang Mao, Mingoo Seok, "Near- and Sub-Vt Pipelines Based onWide-Pulsed-Latch Design Techniques." IEEE journal of solid-state circuits, 2017, pp.2475-2487.

- [5]. S.Dinesh, Christo Ananth, "Area Power and Speed Optimized Serial Type Daisy Chain Memory using modified CPG with SSASP," International Conference on Control, instrumentation, Communication and Computational Technologies (ICCICCT), 2015, pp. 344-349.

- [6]. Nicee staney, anand s, "ptl-and clock-pulse circuit driven novel shift register architecture", 2nd IEEE International Conference On Recent Trends in Electronics Information & Communication Technology (RTEICT), May 19-20, 2017, India, pp. 1072-1079.

- [7]. A. Ghadiri and H. Mahmoodi, "Dual-edge triggered static pulsed flip-flops," in 18th Int. Conf. on VLSI Design Taj Benjal, Kolkata, India, pp. 846-849, 2005.

- [8]. A. Chandrakasan, W. Bowhill, and F. Fox, Design of High-performance Microprocessor Circuits, 1st ed., IEEE Press, Piscataway, 2001.

- [9]. S. D. Naffziger and G. Hammond, "The implementation of the next generation 64b Itanium TM microprocessor," in IEEE International Solid-State Circuits Conference (ISSCC 2002), pp. 344-472, 2002.

- [10]. N. Weste and D. Harris, CMOS VLSI Design: A Circuits and Systems Perspective: Addison Wesley Higher Education, 2005.

- Shefali Sharma and Bipan Kaushal,"Shift Register Design Using Two Bit Flip-Flop", IEEE Proceedings of 2014 RAECS UIET [11]. Panjab University Chandigarh. 2014.

- [12]. P. Zhao, J. McNeely, P. Golconda, M. A. Bayoumi, R. A. Barcenas, and W. Kuang, "Low-Power Clock Branch Sharing Double-Edge Triggered Flip-Flop," Very Large Scale Integration (VLSI) Systems, IEEE Transactions on, vol. 15, pp. 338-345, March 2007.

- Divya Sreenivasan, Devika Purushothaman, Kirti S. Pande and Murty N.S. "Dual-Threshold Single-Ended Schmitt-Trigger Based [13]. SRAM Cell", IEEE International Conference on Computational Intelligence and Computing Research, 2016.

- Mal, A.K. and Todani, R. "Non Overlapping C lock Generator for Switched Capacitor Circuits in Bio-Medical Applications", [14]. International Conference on Signal Processing, Communication, Computing and Networking Technologies 2011.

- Shefali Sharma and Bipan Kaushal,"Shift Register Design Using Two Bit Flip-Flop", IEEE Proceedings of 2014 RAECS UIET [15]. Panjab University Chandigarh. 2014.

- A.V.Ananthalakshmi and G.F.Sudha,"Design of 4-Bit Reversible Shift Registers", WSEAS Trans. on Circuits and Systems. vol. 12, [16]. no. 12, pp.376 385, 2013.

- [17]. S.ehsan razavi, javad royaei, mehdi bahadorzadeh, "design a low current and high speed shift register based on d type flip flop" IEEE .2015

- Mohammad arif sobhan bhuiyan, Arvin mahmoudbeik,torikul islam badal,mamunbin ibne reaz,labonnah ff.rahma, "low power d [18]. flip-flop serial in/parallel out base shift register", International Conference on Advances in Electrical, Electronic and System Engineering, 14-16 Nov 2016, Putrajaya, Malaysia, 2016.

- [19]. Mal, A.K. and Todani, R. "Non Overlapping C lock Generator for Switched Capacitor Circuits in Bio-Medical Applications", International Conference on Signal Processing, Communication, Computing and Networking Technologies 2011. Sujatha, B.V. and Sudha, G.F "An Efficient Design for Reduction of Power Dissipation in Johnson Counter using Clock Gating",

- [20]. International Journal of Science and Research (IJSR), Volume 4 Issue 1, 2013

### Author Biography

1st Suraj Pattanaik – Received the B.Tech. degree in Electronics and Communication Engineering from the University of BPUT, Odisha, in 2014, and the M. Tech. degree in Electronic and Communication Engineering from CAPGS, BPUT, Rourkela, Odisha, in 2018. Currently, He is working as an Assistant Professor of Electronics and communication engineering Dept. at Gandhi Institute for Education and Technology. Asst. Professor Suraj Pattanaik may be reached at Pattanaik.suraj@gmail.com

2nd Suraj Kumar Samal – Received the B.Tech. degree in Electronics and Communication Engineering from the University of BPUT, Odisha, in 2013, and the M. Tech. degree in Electronic and Communication Engineering from the KIIT University, Bhubaneswar, Odisha, in 2017. Currently, He is working as an Assistant Professor in Electronics and communication engineering Dept. at Gandhi Institute for Education and Technology. Asst. Professor Suraj Kumar Samal may be contacted at surajsamal1992@gmail.com